VMESCmodule

VME System Controller Core

Not recommended for new designs. Use VMESCmodule2/2e instead.

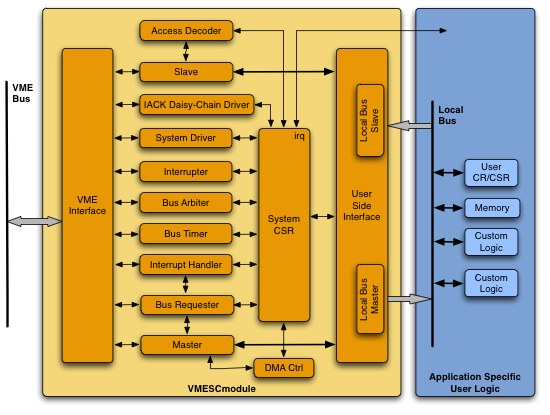

Inicore's VMESCmodule is a VME to local bus bridge containing a VME slave with 4 memory window decoders, a VME master with integrated DMA engine, a programable VME interrupter supporting IRQ1-IRQ7 request levels, an autonomous VME interrupt handler, and a VME system controller. The system controller has a bus arbiter supporting prioritized and round-robin arbitration, a programmable bus timer, a system clock driver, a system reset driver, and an interrupt daisy-chain driver. System controller functionality can be enabled or disabled by using control inputs, or is automatically set when the controller is located in VME slot 1.

All these VME features are complemented by system features such as 4 32-bit mailboxes, 4 7-bit semaphores, interrupt controller, and configuration and status registers. A generic 32-bit wide user-side port connects to local registers and memories and provides access to the cores internal CR/CSR memory space.

With this rich feature set, the core can be used as a System Controller Module, as a Master Module, or as a Slave Module. This makes the VMESCmodule an excellent platform to base all your future VME designs on.

Block Diagram

Features

System Controller

- Bus Arbiter

- Bus Timer

- SYSCLOCK* driver

- SYSFAIL* driver

- First Slot Detector

- IACK daisy-chain driver

Master Interface

- Addressing modes: A16, A24, A32

- Data modes: D8(EO), D16, D32, D32-BLT, D64-MBLT

- Supports data read-ahead and posted write to increase throughout

- Constant local bus address for DMA transfers to/from FIFOs

Slave Interface

- Addressing modes: A16, A24, A32

- Data types: D8(EO), D16, D32, D32-BLT, D64-MBLT

- Access modes: Read, write, read-modify-write

- Selectable rescinding DTACK

Interrupt Handler

- Automatically fetches STATUS/ID vector from pending VME interrupt requests

- Supports D08(O), D16, and D32

Interrupter

- D08(O) interrupt status vector

- Software interrupt request (ROAK)

- User interrupt request (RORA)

- Programmable interrupt level

Bus Requester

- Supports RWD (release when done) and ROR (release on request) arbitration schemes

- FAIR requester

- Supports early withdrawal of bus request

System CR/CSR

- Contains address decoding for CR/CSR space

- Accessible via VME and local bus

- Local status and configuration regs for

- Interrupter

- Interrupt handler

- Slave memory windows

- DMA operation

- Special functions

- 4 32-bit mailbox registers

- 4 8-bit semaphores

- Local interrupt controller

- VME interrupt controller

Local Bus Interface

- Fully synchronous bus interface for user logic

- User selectable wait-states

- Optional big-endian to little-endian conversion

Highlights

- VME Master

- VME Slave

- VME System Controller

- VME to Local Bus Bridge

Documentation

Utilization Numbers

Please contact us for utilization number.